题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知集成移位寄存器的逻辑符号及引脚图如图4-68所示,试列出功能表。

已知集成移位寄存器的逻辑符号及引脚图如图4-68所示,试列出功能表。

1.jpg)

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

已知集成移位寄存器的逻辑符号及引脚图如图4-68所示,试列出功能表。

1.jpg)

答案

答案

更多“已知集成移位寄存器的逻辑符号及引脚图如图4-68所示,试列出功能表。”相关的问题

更多“已知集成移位寄存器的逻辑符号及引脚图如图4-68所示,试列出功能表。”相关的问题

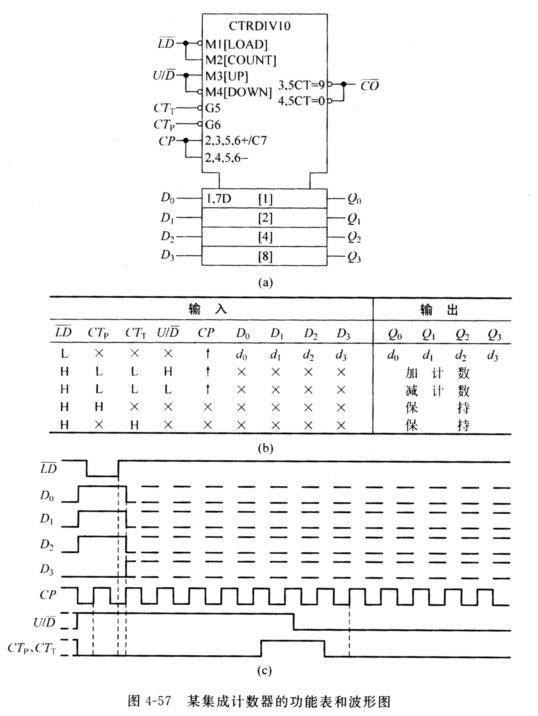

第1题

已知某十进制集成计数器的逻辑符号及功能表如图4-57(a)、(b)所示,试画出在图4-57(c)所示输入信号作用下Q0、Q1、Q2、Q3及

的输出波形。

的输出波形。

第2题

TTL集成施密特触发器CTll32的逻辑符号和vI一vO曲线如图9.6.1(a)所示,图(b)为CTll32组成的电路。 (1)说明电路具有什么功能。 (2)定性画出VA,VO的波形。 (3)若R=10 kΩ,C=0.01μF,计算工作周期。

.jpg)

第3题

集成DAC器件AD7520电路如图题8.6所示,其应用电路如图题8.9所示。已知AD7520参数:电源电压为+5V~+15V,分辨率为10位,稳定时间为500ns。为得到±5V的最大输出模拟电压,试确定基准电压VREF、偏移电压VB及偏移电阻RB,并列出高三位(含符号位)输入输出对照表。

第4题

分别是四个D触发器的输出端。四个D触发器的CP端连接在一起,从9脚引出。

分别是四个D触发器的输出端。四个D触发器的CP端连接在一起,从9脚引出。 端(引脚1)是公共的直接清零端,当

端(引脚1)是公共的直接清零端,当 =0时,1Q~4Q均0。现用此集成芯片构成移位寄存器,试画出在下列两种情况下芯片外引脚之间的连接图:

=0时,1Q~4Q均0。现用此集成芯片构成移位寄存器,试画出在下列两种情况下芯片外引脚之间的连接图:

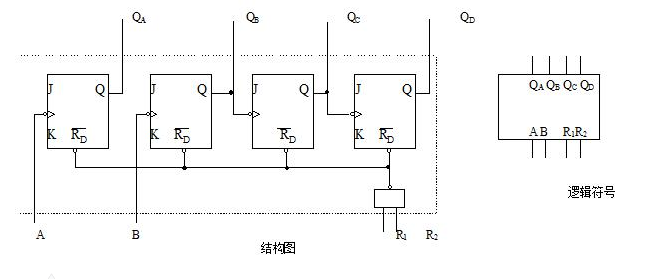

第5题

已知某集成计数器的结构图及逻辑符号如图所示,虚线以内为集成电路的内部电路。要求:

(1)单片计数器能实现的最大模值为多少;

(1)单片计数器能实现的最大模值为多少;

(2)画出用该计数器实现五进制计数器的逻辑图;

(3)画出用该计数器实现六进制计数器的逻辑图;

(4)画出用该计数器实现三十进制计数器的逻辑图。

第6题

写出如图52集成译码器T4139输出

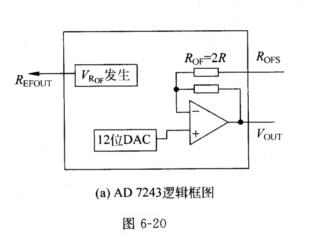

第8题

图(a)是AD7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0→+10V,请读者增加适当的引脚连接线,使之成为-5V→+5V双极性输出的DAC,并说明理由。

第9题

图6-20(a)是AD 7243逻辑框图,它是一种可供用户由单极性扩展为双极性的DAC集成芯片,单极性输出为0→+10V,请读者增加适当的引脚连接线,使之成为一5V→+5V双极性输出的DAC,并说明理由。

第10题

图10.4.1所示电路是用十位集成R-2R倒T型数模转换器CB7520和74LS161组成的波形发生器电路。已知CB7520参考电压VREF=-10 V,请求出vO的值,CB7520的电路结构如图10.3.2所示。

1.jpg)

第11题

1.jpg)