题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

图是一个序列信号产生电路,由一个计数器和一个PLA组成,(PLA组成的电路是一个数据选择器),CP是方波时钟信号。

图是一个序列信号产生电路,由一个计数器和一个PLA组成,(PLA组成的电路是一个数据选择器),CP是方波时钟信号。试画出QA~QD和f信号的波形(要求超过一个计数周期)。

答案

答案

查看答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

图是一个序列信号产生电路,由一个计数器和一个PLA组成,(PLA组成的电路是一个数据选择器),CP是方波时钟信号。试画出QA~QD和f信号的波形(要求超过一个计数周期)。

答案

答案

更多“图是一个序列信号产生电路,由一个计数器和一个PLA组成,(PLA组成的电路是一个数据选择器),CP是方波时钟信号。”相关的问题

更多“图是一个序列信号产生电路,由一个计数器和一个PLA组成,(PLA组成的电路是一个数据选择器),CP是方波时钟信号。”相关的问题

第1题

第4题

图3.72所示的是一个正弦和余弦序列发生器的信号流程图,其中,延时器1和延时器2的输入和输出信号分别为s1(n+1)、s1(n)和s2(n+1)、s2(n)。

第7题

第8题

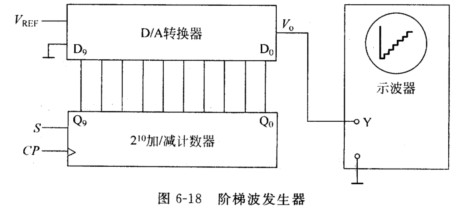

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

第9题