题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

下列元件中输出端可以呈高阻状态的是?

A、传输门

B、与非门

C、或非门

D、开漏输出门

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

A、传输门

B、与非门

C、或非门

D、开漏输出门

答案

答案

更多“下列元件中输出端可以呈高阻状态的是?”相关的问题

更多“下列元件中输出端可以呈高阻状态的是?”相关的问题

第1题

图2.4.2(a)、(b)所示电路都是CMOS门电路,指出门输出Y1、Y2、Y3为高阻(Z)状态时各个对应输入端分别为何逻辑值。

第2题

设输入变量为A、B、C、D、E、F、G、H、I,用图中所示的PAL16L8实现逻辑函数X、Y、Z的表达式分别为

X=

Y=ABG+

Z=

试画出编程后的逻辑电路。

第3题

四总线缓冲器的设计

实验要求

用原理图输入设计法或Verilog HDL文本输入设计法设计四总线缓冲器(CT74125)电路,建立四总线缓冲器的实验模式。通过电路仿真和硬件验证,进一步了解四总线缓冲器的功能和特性。

设计原理

四总线缓冲器CT74125的元件符号如图所示,输入端为A(A4~A1),输出端为Y(Y4~Y1),ENN是使能控制输入端,低电平有效,当ENN=0时,输出Y=A;当ENN=1时Y=Z(高阻态)。

第5题

A.数字频率与模拟频率之间呈线性关系

B.能将稳定的模拟滤波器映射为一个稳定的数字滤波器

C.使用的变换是s平面到z平面的多值映射

D.可以用于设计低通、高通和带阻等各类滤波器

第10题

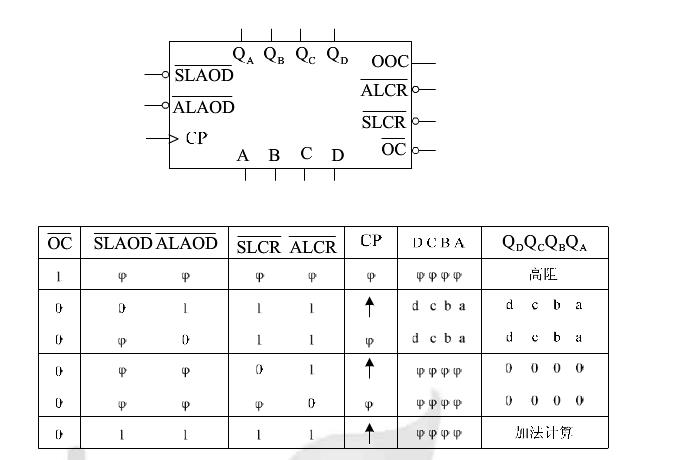

74ALS561是一种功能较为齐全的同步计数器。其内部是4位二进制计数器。功能表和引脚示意图如图所示(QD为高位输出)。其中 为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。

为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。