题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

一位二进制计数器,其输出频率f0是输入频率f的1£¯2,称为四分频器。()

答案

答案

请输入或粘贴题目内容

搜题

请输入或粘贴题目内容

搜题

拍照、语音搜题,请扫码下载APP

拍照、语音搜题,请扫码下载APP

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

答案

答案

更多“一位二进制计数器,其输出频率f0是输入频率f的1£¯2,称为四分频器。()”相关的问题

更多“一位二进制计数器,其输出频率f0是输入频率f的1£¯2,称为四分频器。()”相关的问题

第1题

图所示电路是低频信号发生器中常用的一种电路,称为R-C选频网络。当输入电压

第2题

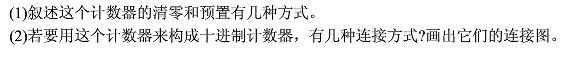

74ALS561是一种功能较为齐全的同步计数器。其内部是4位二进制计数器。功能表和引脚示意图如图所示(QD为高位输出)。其中 为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。

为输出高阻控制端,OOC是与时钟同步的进位输出,其他各输入、输出端的功能可由功能表得知。

第3题

假设LC并联谐振回路的Q值很大,其中心频率为f0,两个3dB截止频率分别为f1和f2,已知输入电流为调幅波ii(t)=I0(1+macos2πFt)cos2πf0t,其中BW3dB=2F,求输出电压。

第5题

第7题

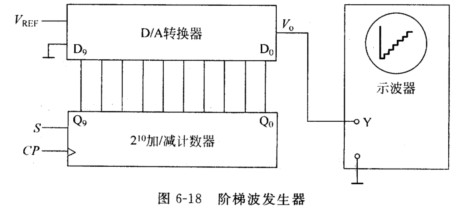

如图所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。

第8题

A.错误

B.正确

第9题

已知一阶环正弦鉴相器输出最大电压Vd=2.5V,VCO的灵敏度Kω=104Hz/V,VCO自由振荡频率f0=1MHz,试问:当输入信号为vi(t)=2sin(1.96π×106t+30°)V时,环路能否锁定?试画出相图说明。若能锁定,稳态相差有多大?此时控制电压等于多少?

第10题

逆均匀洗牌函数得到输出端地址的方法是把输入端二进制地址()。

A.循环左移一位

B.循环右移一位

C.从第k位开始的低端地址部分循环左移一位

D.从最高位至第n-k-1位的高端地址部分循环左移一位

第11题

图6-18所示电路可用作阶梯波发生器。如果计数器是加/减计数器,它和DAC相适应,均是十位(二进制数),时钟频率为1 MHz,求阶梯波的重复周期,试画出加法计数和减法计数时DAC的输出波形(控制信号S=0,加计数;S=1,减计数)。